Дипломная работа: Анализ алгоритма работы специализированного вычислителя

Дипломная работа: Анализ алгоритма работы специализированного вычислителя

ДИПЛОМНАЯ РАБОТА НА ТЕМУ:

Анализ алгоритма работы специализированного вычислителя

ВВЕДЕНИЕ

В настоящее время в развитии микроэлектроники, как в России, так и за

рубежом прошел определенный этап, который позволил по иному посмотреть на

проектирование современных радиотехнических приборов.

Возросла сложность приборов, но заметно уменьшились их

габариты, что отражает общее развитие микроэлектронной элементной базы. Одну из

ведущих ролей стали играть процессорные технологии, широко применяется цифровая

обработка.

Современная система регистрации данных – это

высокопроизводительный вычислитель, имеющий в своей основе процессор либо

контроллер, накопитель информации большого объёма и высокоскоростные интерфейсы

связи.

При построении системы регистрации необходимо

учитывать все современные тенденции развития микроэлектроники. В первую очередь

это микросхемы энергонезависимой памяти большого объёма. Прогресс именно в этой

области позволяет построить компактную либо встраиваемую систему регистрации.

Последние доступные решения в области микроконтроллеров позволяют применять

такие интерфейсы как USB. В качестве основного звена, позволяющего совместить

различные по интерфейсам узлы, могут применяться программируемые логические

матрицы. Одна такая микросхема заменит десятки дискретных элементов, тем самым

резко сокращая размеры системы регистрации. При этом потребляемая мощность

будет минимальна и появится гибкость при построении аппаратной части.

1. АНАЛИЗ ИСХОДНЫХ ДАННЫХ

1.1 Анализ алгоритма работы

специализированного вычислителя

Основным требованием, которое должно соблюдаться при

осуществлении сопряжения разрабатываемой системы регистрации входных сигналов и

промежуточных результатов обработки сигналов со специализированным

вычислителем, является обеспечение штатного функционирования

специализированного вычислителя без существенного ухудшения его динамических

характеристик (не более 3 %).

В штатной работе специализированный вычислитель

проводит измерения высоты и составляющих вектора путевой скорости с частотой 33

Гц. Цикл измерения разбит на два этапа:

- излучение и обработка результатов высотомерного

канала;

- излучение и обработка результатов скоростного

канала.

На рисунке 1.1 приведена циклограмма функционирования специализированного

вычислителя. Из рисунка 1.1 видно, что процесс подготовки пакета скоростного

канала, его излучения распределен по трем циклам работы специализированного

вычислителя, в то время как выдача массива в разрабатываемую систему

осуществляется в каждом цикле. На циклограмме работы показаны моменты времени,

в которые вычислитель готов передать блок информации, относящийся к данному

измерению. Из этого следует, что цикл работы разрабатываемого блока от приема

информации до момента готовности принять очередной блок данных должен быть

меньше 30 мс.

Такие исходные данные, как число импульсов в сеансе

излучения, длительность излучения, период повторения импульсов, влияют на

размер передаваемого блока информации. Передача информации из процессора

1879ВМ1 производится при помощи байтного скоростного интерфейса.

Скорость передачи информации составляет до 20 Мб/с.

Работа этого интерфейса замедляет процессор на (12,5 – 15) %. Оптимальное время

передачи информации составляет не более 5 мс, что приведет к снижению

быстродействия системы на 2,5 %.

1.2

Выбор перечня и объема регистрируемой информации

Процессор ячейки АЦП-079-03, входящей в состав специализированного

вычислителя, оперирует 32-х разрядными словами. Поэтому, данные,

предназначенные для передачи от ячейки АЦП-079-03 к разрабатываемой системе

регистрации данных, будут иметь минимальный размер, равный одному слову

микропроцессора (32 бита).

Пакет данных для записи передается в систему регистрации данных на каждом

цикле работы специализированного вычислителя. Для реализации последующей обработки

информации, полученной в ходе испытаний, необходимо разделить пакеты между

собой. Для этого каждый пакет начинается с определенного кода, являющегося

признаком начала пакета и номера пакета. Также имеет смысл записывать

внутреннее системное время специализированного вычислителя. Таким образом, для

однозначной идентификации записанного пакета данных необходимы три следующих

параметра:

-

признак начала пакета данных. Для исключения случайного совпадения кода начала

пакета с данными, признак начала пакета должен иметь размер равный двум словам

микропроцессора (8байт);

-

номер пакета. Исходя из условий технического задания, система

регистрации данных должна обеспечивать время записи до 1 часа. При частоте

прихода пакетов 1/33мс максимальное количество принимаемых пакетов будет

порядка 11000 что меньше максимального числа, которое можно задать при помощи

32-х разрядного двоичного кода. Следовательно, для номера пакета можно

использовать 1 слово микропроцессора (4 байта);

-

системное время. Для передачи системного времени достаточно 1 слова

микропроцессора (4 байта).

Для полного анализа работы высотомера наряду с

результатами обработки полученных данных необходимо также иметь априорные

данные.

Априорные данные вертикального канала приведены в

таблице 1.1.

Таблица 1.1 – Априорные данные вертикального канала.

| Длина, байт |

Переменная |

Назначение |

| 4 |

Regim |

Режим работы изделия |

| 4 |

Regim_RV |

Разновидность режима работы |

| 4 |

CodFwrk |

Код частоты |

| 4 |

Diapazon |

Номер диапазона вертикального

канала |

| 4 |

CodLongAM |

Длительность зондирующих импульсов |

| 4 |

Blank |

Признак «бланкирования» прямого

сигнала |

| 4 |

CodNonius |

Код нониуса |

| 4 |

Hmin |

Начало интервала слежения (поиска) |

| 4 |

Hmax |

Конец интервала слежения (поиска) |

| 4 |

KolDirok |

Количество шумовых стробов в

«свертке» сигнала |

| 4 |

L0 |

Смещение начала «свертки» в пакете |

| 4 |

Lsm |

Ширина интервала построения

«свертки» |

| 4 |

CodARU |

Код АРУ |

| 4 |

Cod_AR |

Код АР (подавления мощности

излучения) |

| 4 |

Cod_IZ |

Код ИЗ (подавления мощности

излучения) |

Переменные, хранящие результаты обработки

вертикального канала, приведены в таблице 1.2.

Таблица 1.2 – Переменные, хранящие результаты обработки вертикального

канала.

| Длина, байт |

Переменная |

Назначение |

| 4 |

SysRg |

Регистр управления |

| 4 |

Matr |

Матрица состояния изделия |

| 4 |

Prizn |

Регистр признаков |

| 4 |

Hi |

Усредненная оценка высоты |

| 4 |

Hirv |

Мгновенная оценка высоты |

| 4 |

Num_Swr |

Количество отсчетов в «свертке»

сигнала |

| 4 |

Num_K |

Количество обрабатываемых точек для

доплеровского фильтра |

| 4 |

FlagACP |

Признак перегрузки АЦП |

| 4 |

Max_Swr |

Положение максимума «свертки» |

| 4 |

Over_Min |

Количество переполнения АЦП снизу |

| 4 |

Over_Max |

Количество переполнения АЦП сверху |

| 4 |

Nap |

Количество точек аппроксимации

фронта |

| 4 |

Im |

Номер отсчета 1-го превышения

порога |

| 4 |

Nap_F |

Признак аппроксимации фронта |

| 4 |

Zahvat |

Признак захвата сигнала

вертикального канала |

| 4 |

LngZhv |

Признак исправности вертикального

канала |

| 4 |

CntZhv |

Количество захватов сигнала

вертикального канала |

| 4 |

Num_Usr |

Максимальное количество усреднений

оценок высоты |

| 4 |

P_Beg |

Указатель начала магазина оценок

высоты |

| 4 |

P_End |

Указатель конца магазина оценок

высоты |

| 4 |

Tek_Usr |

Количество усреднений оценок высоты |

| 4 |

Tek_K0 |

Коэффициент для прогнозирующего

фильтра оценок высоты |

| 4 |

Tek_K1 |

Коэффициент для прогнозирующего

фильтра оценок высоты |

| 4 |

Hv |

Высота волны |

| Длина, байт |

Переменная |

Назначение |

| 4 |

STimer |

Период записи оценок высоты |

| 4 |

ATimer |

Период записи оценок высоты (грубо) |

| 4 |

CntRez |

Счетчик количества измерений Hволны |

| 4 |

FlagSM |

Признак «суша/море» |

| 4 |

Nak_ARU |

Максимальное значение «свертки» для

регулировки АРУ |

| 4 |

Max_ARU |

Порог для изменения шага

регулировки АРУ |

| 4 |

Min_ARU |

Порог для изменения шага

регулировки АРУ |

| 1024 |

Swertka |

«Свертка» сигнала вертикального

канала |

|

|

|

|

Переменные, хранящие априорные данные скоростного канала, приведены в

таблице 1.3.

Таблица 1.3 – Переменные, хранящие априорные данные скоростного канал.

| Длина, байт |

Переменная |

Назначение |

| 4 |

Regim_SS |

Признак измерения скорости |

| 4 |

ModeAK |

Режим измерения скорости (обычный

или в неоднозначности) |

| 4 |

DeltaAK |

Программный нониус |

| 4 |

Lsm_signal |

Сигнальный строб скоростного канала |

| 4 |

Lsm_noise |

Шумовой строб скоростного канала |

| 4 |

Nsm_SS |

Программный нониус |

| 4 |

Nu_Vob_I |

Код вобуляции в пакете |

| 4 |

Nu_Vob_F |

Усредненный код вобуляции |

| 4 |

Ntau0_SS |

Среднее значение транспортных

задержек |

| 4 |

Flag_Sdv_BKF |

Признак необходимости пересчета ВКФ |

Переменные, хранящие результаты обработки принятых данных по скоростному

каналу, приведены в таблице 1.4.

Таблица 1.4 – Переменные, хранящие результаты

обработки принятых данных.

| Длина, байт |

Переменная |

Назначение |

| 4 |

MiddleVobI |

Средний период повторения импульсов

в пакете |

| 4 |

MiddleVobF |

Средний период повторения импульсов

после межпакетного усреднения |

| 4 |

SpecRegim |

Признак спецрежима для скоростного

канала |

| 4 |

OverDataBKF |

Счетчик переполнения АЦП в

скоростном канале |

| 4 |

Dsp1 |

Дисперсия сигнала, принятого 1-й

антенной |

| 4 |

Dsp2 |

Дисперсия сигнала, принятого 2-й

антенной |

| 4 |

Dsp3 |

Дисперсия сигнала, принятого 3-й

антенной |

| 4 |

Li |

Признак отбраковки ВКФ по дисперсии |

| 4 |

L_Signal |

Общий признак отбраковки ВКФ по

дисперсии |

| 4 |

P_BKF_Beg |

Указатель начала магазина ВКФ |

| 4 |

P_BKF_End |

Указатель конца магазина ВКФ |

| 4 |

Tek_BKF_Usr |

Количество усреднений ВКФ |

| 4 |

Step_BKF_Usr |

Изменение количества усреднений ВКФ |

| 4 |

Zero_F_BKF_SS |

Зарезервировано |

| 4 |

N_zhv_SS |

Количество захватов в скоростном

канале |

| 4 |

Zahvat_SS |

Признак захвата сигнала в

скоростном канале |

| 4 |

LngZhv_SS |

Признак исправности скоростного

канала |

| 4 |

Cnt_Zahvat_SS |

Счетчик захватов в скоростном

канале |

| 4 |

F_Max_SS12 |

Максимум 1-й ВКФ |

| 4 |

F_Max_SS23 |

Максимум 2-й ВКФ |

| 4 |

N_Max_SS12 |

Положение максимума 1-й ВКФ |

| 4 |

N_Max_SS23 |

Положение максимума 2-й ВКФ |

| 4 |

M_Wide_SS12 |

Положение левой границы 1-й ВКФ по

уровню 0,5 от максимума |

| 4 |

P_Wide_SS12 |

Положение правой границы 2-й ВКФ по

уровню 0,5 от максимума |

| 4 |

M_Wide_SS23 |

Положение левой границы 1-й ВКФ по

уровню 0,5 от максимума |

| 4 |

P_Wide_SS23 |

Положение правой границы 2-й ВКФ по

уровню 0,5 от максимума |

| 4 |

No_Koso_12 |

Признак запрета анализа искажения

1-й ВКФ |

| 4 |

No_Koso_23 |

Признак запрета анализа искажения

2-й ВКФ |

| 4 |

Wide1_SS |

Ширина 1-й ВКФ |

| 4 |

Wide2_SS |

Ширина 2-й ВКФ |

| 4 |

Ntau1_SSF |

Транспортная задержка для 1-й ВКФ |

| 4 |

Ntau2_SSF |

Транспортная задержка для 2-й ВКФ |

| 4 |

Ntau1_SS |

Транспортная задержка для 1-й ВКФ с

учетом ограничений |

| 4 |

Ntau1_SS |

Транспортная задержка для 2-й ВКФ с

учетом ограничений |

| 4 |

NtauF_1 |

Усредненная транспортная задержка

для 1-й ВКФ |

| 4 |

NtauF_2 |

Усредненная транспортная задержка

для 2-й ВКФ |

| 4 |

DelatNtau |

Поправка для суммы транспортных

задержек |

| 4 |

SpeedVx |

Продольная скорость |

| 4 |

SpeedVy |

Вертикальная скорость |

| 4 |

SpeedVz |

Поперечная скорость |

| 4 |

Bsn |

Угол сноса |

| 4 |

SpeedVxi |

Мгновенное значение продольной

скорости |

| 4 |

SpeedVzi |

Мгновенное значение поперечной

скорости |

| 4 |

Bsni |

Мгновенное значение угла сноса |

| 4 |

SpeedVzF |

Усредненная продольная скорость |

| 4 |

BsnF |

Усредненный угол сноса |

| 4 |

P_Beg_SS |

Указатель начала магазина оценок

продольной скорости |

| 4 |

P_End_SS |

Указатель конца магазина оценок

продольной скорости |

| 4 |

Tek_Usr_SS |

Количество усреднений в продольном

канале |

| 4 |

Step_Usr_SS |

Изменение количества усреднений в

продольном канале |

| 4 |

Tek_K0_SS |

Коэффициент для прогнозирующего

фильтра оценок продольной скорости |

| 4 |

Tek_K1_SS |

Коэффициент для прогнозирующего

фильтра оценок продольной скорости |

| 64 |

F_BKF12_SS |

1-я ВКФ |

| 64 |

F_BKF23_SS |

2-я ВКФ |

| 2048 |

– |

Сигнал скоростного канала (1-й

срез) |

| 2048 |

– |

Сигнал скоростного канала (2-й

срез) |

| 2048 |

– |

Сигнал скоростного канала (3-й

срез) |

| 2048 |

– |

Сигнал скоростного канала (4-й

срез) |

| 2048 |

– |

Сигнал скоростного канала (5-й

срез) |

| 2048 |

– |

Сигнал скоростного канала (6-й

срез) |

| 2048 |

– |

Сигнал скоростного канала (7-й

срез) |

В итоге суммарный объем одного пакета информации получается равным 16

кбайт. В систему регистрации информации пакеты приходят с частотой 33 Гц,

следовательно, за 1 час работы системы в нее придет 110 тыс. пакетов

информации. Исходя из общего времени записи информации получается необходимый

объем накопителя

Vнак= 16 кбайт · 110 тыс. пакетов » 2Гб.

Для повышения надежности хранения информации, применим

запись информации с двойным резервированием, следовательно, необходимый объем

накопителя увеличится в два раза и составит 4 Гб.

1.3

Анализ конструкции

Разрабатываемая конструкция предназначена для сохранения в процессе

натурных испытаний специализированного вычислителя информации. Блок должен быть

совместим как механически, так и электрически с ячейкой специализированного

вычислителя АЦП-079-03 и встраиваться в уже готовое изделие А-079, либо

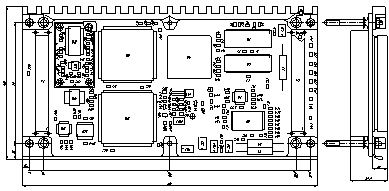

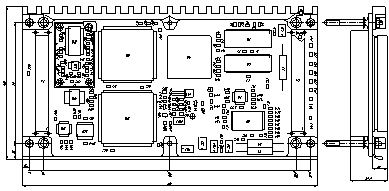

А-079-01. На рисунке 1.2 представлен эскиз ячейки специализированного

вычислителя АЦП-079-03.

Рисунок 1.2 – Эскиз ячейки специализированного

вычислителя АЦП-079-03

Ячейка АЦП-079-03 состоит из многослойной печатной

платы размером 180´90 мм, шести фиксированных точек, через которые при

помощи винтов осуществляется крепление ячейки, и двух сигнальных разъемов Х1 и

Х2 – типа ESQT-130-02-G-Q-368 с направляющими ATS-30-Q.

В таблицах 1.5 и 1.6 представлены контакты разъемов

Х1, Х2 и соответствующие им сигналы.

Таблица 1.5 – Разъем Х1

| Контакт |

Цепь |

Контакт |

Цепь |

Контакт |

Цепь |

| 1 |

Корпус |

9 |

ГД12 |

17 |

ТМ НРВ |

| 2 |

Корпус |

10 |

ГД1 |

18 |

УПР АРУ |

| 3 |

Корпус |

11 |

ГД2 |

19 |

УПР АР |

| 4 |

Корпус |

12 |

- |

20 |

ТМ АР |

| 5 |

ГД13 |

13 |

Корпус |

21 |

ТМ АРУ |

| 6 |

ГД0 |

14 |

Корпус |

22 |

- |

| 7 |

- |

15 |

Корпус |

23 |

- |

| 8 |

- |

16 |

Корпус |

24 |

- |

| 25 |

Корпус |

51 |

Корпус |

77 |

Корпус |

| 26 |

Корпус |

52 |

Корпус |

78 |

Корпус |

| 27 |

Корпус |

53 |

ТМ Видео 2 |

79 |

Корпус |

| 28 |

Корпус |

54 |

INITM5 |

80 |

Корпус |

| 29 |

ГД15 |

55 |

INITM4 |

81 |

Импульс мод. 1 |

| 30 |

ГД3 |

56 |

ТМ Видео 1 |

22 |

Импульс мод. 2 |

| 31 |

ГД4 |

57 |

INITM2 |

23 |

ВИ1 |

| 32 |

ГД11 |

58 |

INITM3 |

84 |

ВИ2 |

| 33 |

ГД7 |

59 |

INITM1 |

85 |

Корпус |

| 34 |

ГД14 |

60 |

INITM0 |

86 |

Корпус |

| 35 |

ГД5 |

61 |

Корпус |

87 |

Корпус |

| 36 |

ГД10 |

62 |

Корпус |

88 |

Корпус |

| 37 |

Корпус |

63 |

Корпус |

89 |

ГД8 |

| 38 |

Корпус |

64 |

Корпус |

80 |

ГД6 |

| 39 |

Корпус |

65 |

Сброс КО |

91 |

ГД9 |

| 40 |

Корпус |

66 |

Запись |

92 |

- |

| 41 |

ТМХ1 |

67 |

- |

93 |

Корпус |

| 42 |

ТМХ2 |

68 |

- |

94 |

Корпус |

| 43 |

ТМХ3 |

69 |

А3 |

95 |

Корпус |

| 44 |

ТМХ4 |

70 |

10МНZ |

96 |

Корпус |

| 45 |

Моделиро-вание |

71 |

- |

97 |

ИЗ2 |

| 46 |

- |

72 |

- |

38 |

КАПРМ |

| 47 |

ТМХ5 |

73 |

А1 |

99 |

Мод. АМ |

| 48 |

ТМХ0 |

74 |

А2 |

100 |

Резерв |

| 49 |

Корпус |

75 |

Выход КО |

101 |

ФМ2 |

| 50 |

Корпус |

76 |

Чтение |

102 |

ФМ1 |

| 103 |

КАПП |

109 |

ИЗ1 |

115 |

КЧ2 |

| 104 |

ВСК |

110 |

КАПРМ1 |

116 |

КЧ1 |

| 105 |

Корпус |

111 |

КАПРМ2 |

117 |

Корпус |

| 106 |

Корпус |

112 |

АМ |

118 |

Корпус |

| 107 |

Корпус |

113 |

КЧ4 |

119 |

Корпус |

| 108 |

Корпус |

114 |

КЧ3 |

120 |

Корпус |

Таблица 1.6 – Разъем Х2

| Контакт |

Цепь |

Контакт |

Цепь |

Контакт |

Цепь |

| 1 |

Корпус |

19 |

Корпус |

37 |

D7 |

| 2 |

Корпус |

20 |

Корпус |

38 |

K D2 |

| 3 |

Корпус |

21 |

D1 |

39 |

AS |

| 4 |

Корпус |

22 |

Корпус |

40 |

DS |

| 5 |

WAIT |

23 |

+5BI |

41 |

K AS |

| 6 |

Корпус |

24 |

+5BI |

42 |

K D1 |

| 7 |

+15В |

25 |

WRITE |

43 |

K D7 |

| 8 |

+15В |

26 |

Корпус |

44 |

D6 |

| 9 |

- |

27 |

Корпус |

45 |

J2_TMS |

| 10 |

Корпус |

28 |

Корпус |

46 |

J2_TCK |

| 11 |

-15В |

29 |

J1_TCK_KO |

47 |

J2_TD0 |

| 12 |

-15В |

30 |

J1_TDO_KO |

48 |

J2_TDI |

| 13 |

D5 |

31 |

J1_TDI_KO |

49 |

+5B |

| 14 |

Корпус |

32 |

J1_TMS_KO |

50 |

+5B |

| 15 |

-5BI |

33 |

D4 |

51 |

+5B |

| 16 |

-5BI |

34 |

D3 |

52 |

+5B |

| 17 |

CPU_INIT |

35 |

D0 |

53 |

Корпус |

| 18 |

Корпус |

36 |

D2 |

54 |

Корпус |

| 55 |

Корпус |

78 |

LN6 |

100 |

REZ_RAZ2 |

| 56 |

Корпус |

79 |

K D3 |

101 |

Корпус |

| 58 |

J1_TD0 |

80 |

K D0 |

102 |

Корпус |

| 59 |

J1_TDI |

81 |

LN7 |

103 |

Корпус |

| 60 |

J1_TMS |

82 |

LN1 |

104 |

Корпус |

| 61 |

LN12 |

83 |

- |

105 |

+3.3B |

| 62 |

- |

84 |

ТД2 |

106 |

+3.3B |

| 63 |

K D5 |

85 |

LN5 |

107 |

+3.3B |

| 64 |

K DS |

86 |

LN4 |

108 |

+3.3B |

| 65 |

LN8 |

87 |

RY/BY KO |

109 |

+3.3B |

| 66 |

LN11 |

88 |

- |

110 |

+3.3B |

| 67 |

- |

89 |

K WAIT |

111 |

+3.3B |

| 68 |

+5.5 B II |

90 |

- |

112 |

+3.3B |

| 69 |

LN0 |

91 |

K D6 |

113 |

Корпус |

| 70 |

LN9 |

92 |

ТД3 |

114 |

Корпус |

| 71 |

- |

93 |

K WRITE |

115 |

Корпус |

| 72 |

5.5 B общ. |

94 |

- |

116 |

Корпус |

| 73 |

LN10 |

95 |

- |

117 |

- |

| 74 |

LN2 |

96 |

- |

118 |

ТД |

| 75 |

- |

97 |

K D4 |

119 |

ТД |

| 76 |

-5.5 B II |

98 |

ТД4 |

120 |

Корпус |

| 77 |

LN3 |

99 |

REZ_RAZ1 |

|

|

Электрическое соединение разрабатываемой системы с

платой АЦП-079-03 будет осуществляться при помощи этих разъемов (Х1, Х2).

Входными сигналами системы регистрации данных

являются:

-

шины питания (может использоваться

вся номенклатура питающих напряжений);

-

последовательный байтный порт

микропроцессора LINK (LN0 – LN12).

Исходя из анализа цепей в соединителях Х1 и Х2 получаем, что все

требуемые сигналы находятся на разъеме Х2, следовательно разъем Х1 будет

использоваться только для дублирования цепей корпуса и в качестве механического

соединителя. В таблице 1.6 приведены контакты разъема Х2 разрабатываемой ячейки

и сигналы соответствующие им, которые предполагается использовать для связи с

ячейкой АЦП-079-03.

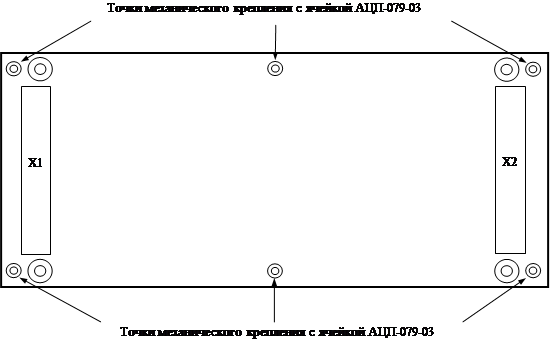

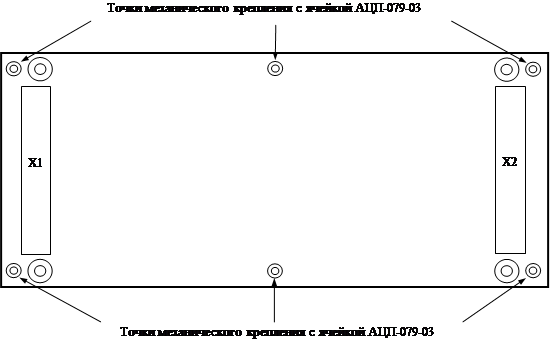

Так как разрабатываемая ячейка будет использоваться в составе

специализированного вычислителя необходимо обеспечить дополнительное

механическое крепление. Следовательно нужно обеспечить совместимость системы

регистрации данных и ячейки АЦП-079-03 по местам механического крепления. Для

осуществления механического крепления ячеек в составе изделия необходимо

использовать крепеж (болты, домкраты) большей длинны. Так как разрабатываемая ячейка будет использоваться в составе

специализированного вычислителя необходимо обеспечить дополнительное

механическое крепление. Следовательно нужно обеспечить совместимость системы

регистрации данных и ячейки АЦП-079-03 по местам механического крепления. Для

осуществления механического крепления ячеек в составе изделия необходимо

использовать крепеж (болты, домкраты) большей длинны.

Страницы: 1, 2, 3

|

Так как разрабатываемая ячейка будет использоваться в составе

специализированного вычислителя необходимо обеспечить дополнительное

механическое крепление. Следовательно нужно обеспечить совместимость системы

регистрации данных и ячейки АЦП-079-03 по местам механического крепления. Для

осуществления механического крепления ячеек в составе изделия необходимо

использовать крепеж (болты, домкраты) большей длинны.

Так как разрабатываемая ячейка будет использоваться в составе

специализированного вычислителя необходимо обеспечить дополнительное

механическое крепление. Следовательно нужно обеспечить совместимость системы

регистрации данных и ячейки АЦП-079-03 по местам механического крепления. Для

осуществления механического крепления ячеек в составе изделия необходимо

использовать крепеж (болты, домкраты) большей длинны.